Evaluating RISC-V Instructions Natively with Narvie (Poster)

Abstract

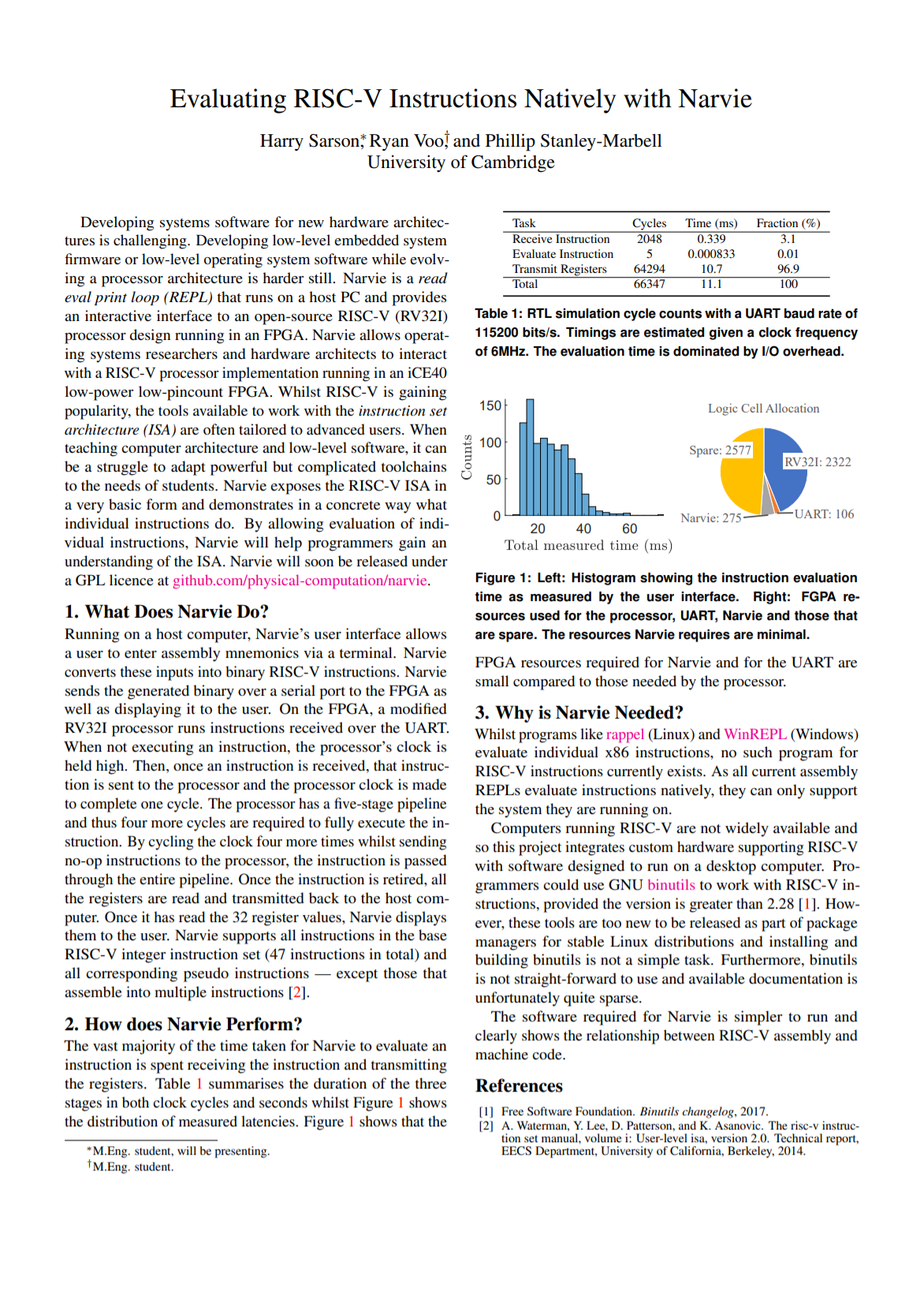

Developing systems software for new hardware architectures is challenging. Developing low-level embedded system

firmware or low-level operating system software while evolving a processor architecture is harder still. Narvie is a read

eval print loop (REPL) that runs on a host PC and provides

an interactive interface to an open-source RISC-V (RV32I)

processor design running in an FPGA. Narvie allows operating systems researchers and hardware architects to interact

with a RISC-V processor implementation running in an iCE40

low-power low-pincount FPGA. Whilst RISC-V is gaining

popularity, the tools available to work with the instruction set

architecture (ISA) are often tailored to advanced users. When

teaching computer architecture and low-level software, it can

be a struggle to adapt powerful but complicated toolchains

to the needs of students. Narvie exposes the RISC-V ISA in

a very basic form and demonstrates in a concrete way what

individual instructions do. By allowing evaluation of individual instructions, Narvie will help programmers gain an

understanding of the ISA.

Cite as:

H. Sarson, R. Voo, and P. Stanley-Marbell, "Evaluating RISC-V Instructions Natively with Narvie", EuroSys 2019 (Poster).

BibTeX:

@inproceedings{Brooks2019SafeguardingSD,

title={Evaluating RISC-V Instructions Natively with Narvie},

author={Sarson,Harry and Voo,Ryan and Stanley-Marbell, Phillip},

year={2019},

title = {EuroSys '19: Proceedings of the Fourteenth EuroSys Conference 2019},

year = {2019},

isbn = {9781450362818},

publisher = {Association for Computing Machinery},

address = {New York, NY, USA},

location = {Dresden, Germany}

}