Synthesizing Compact Hardware for Accelerating Inference from Physical Signals in Sensors

Abstract

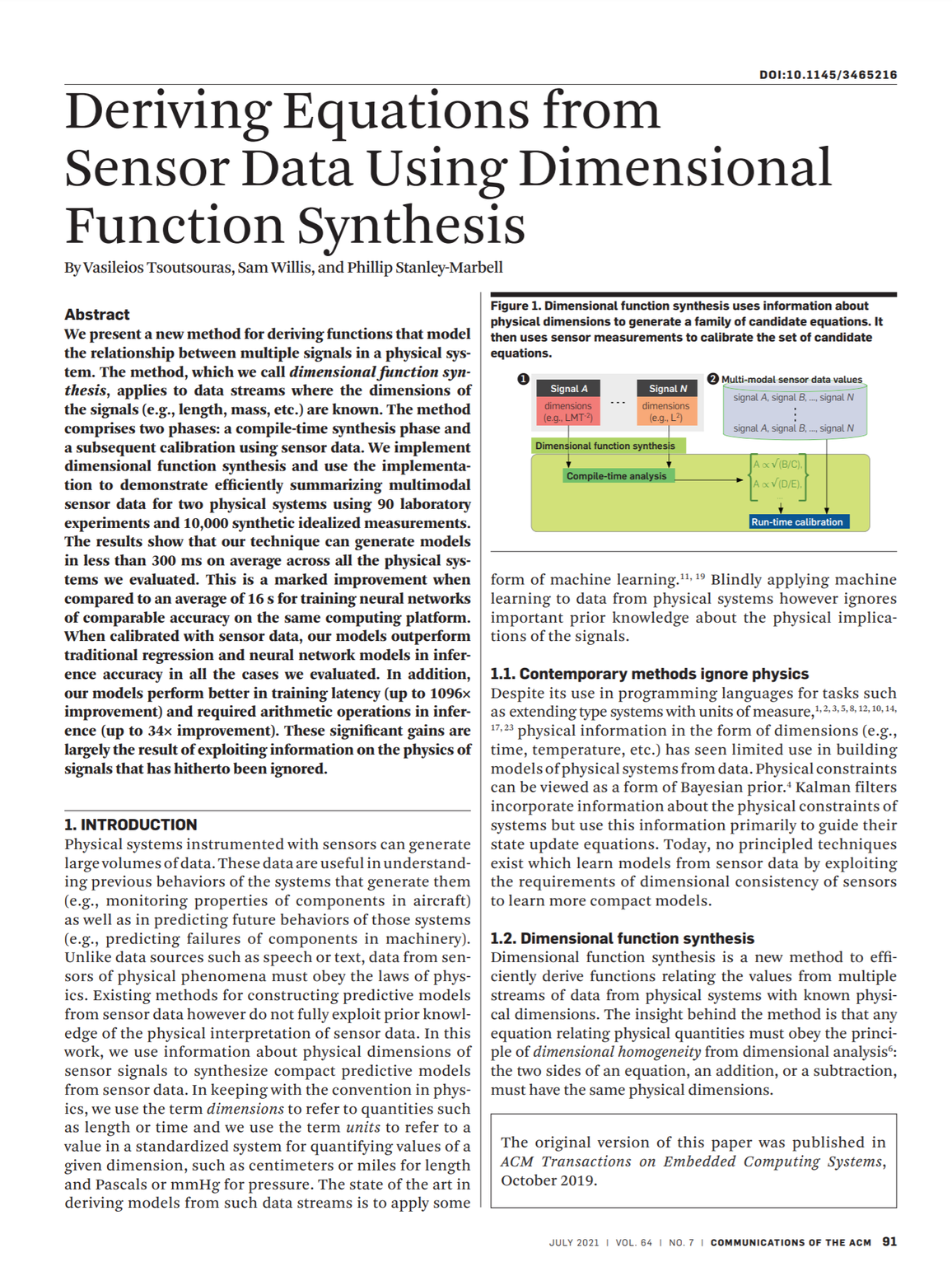

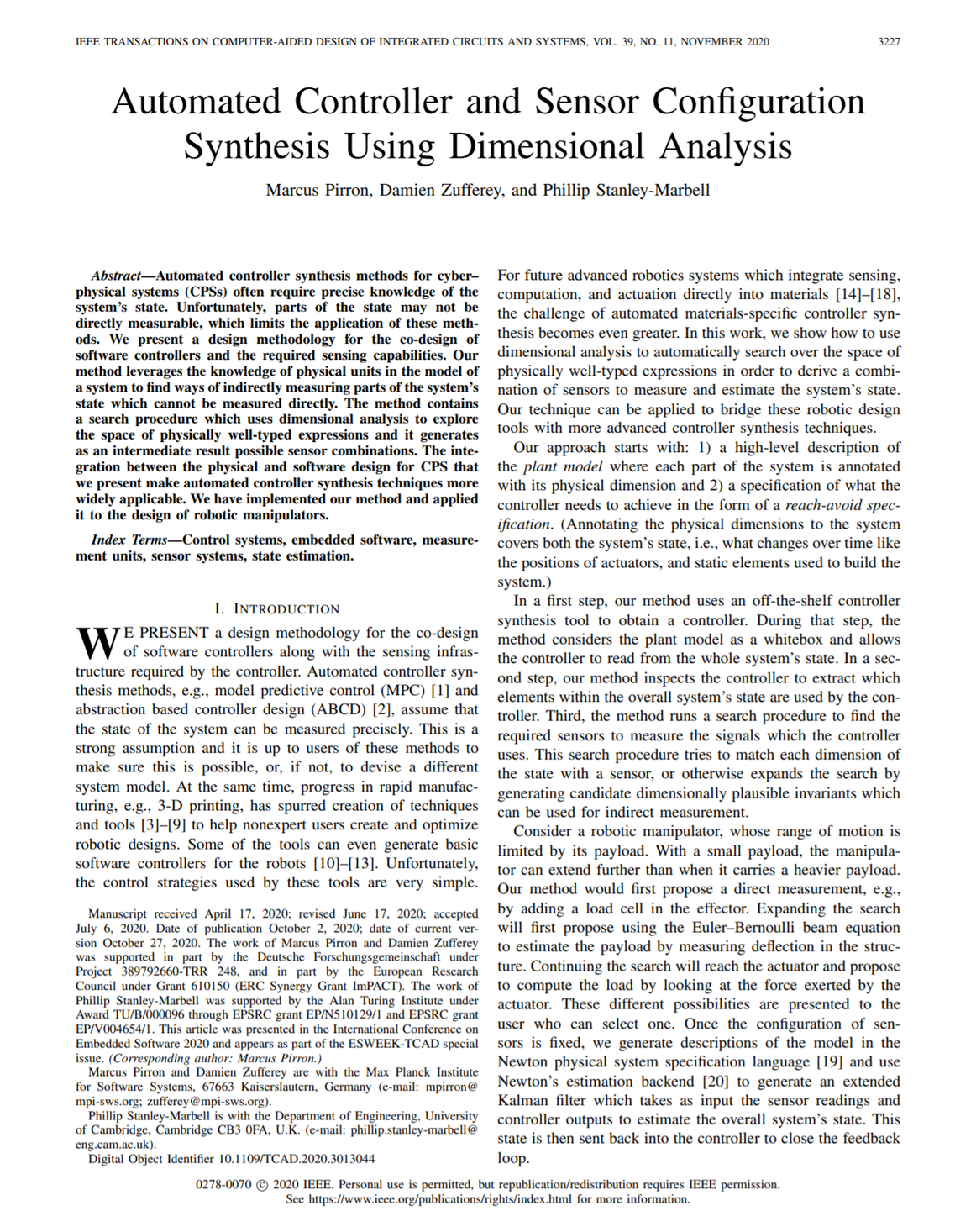

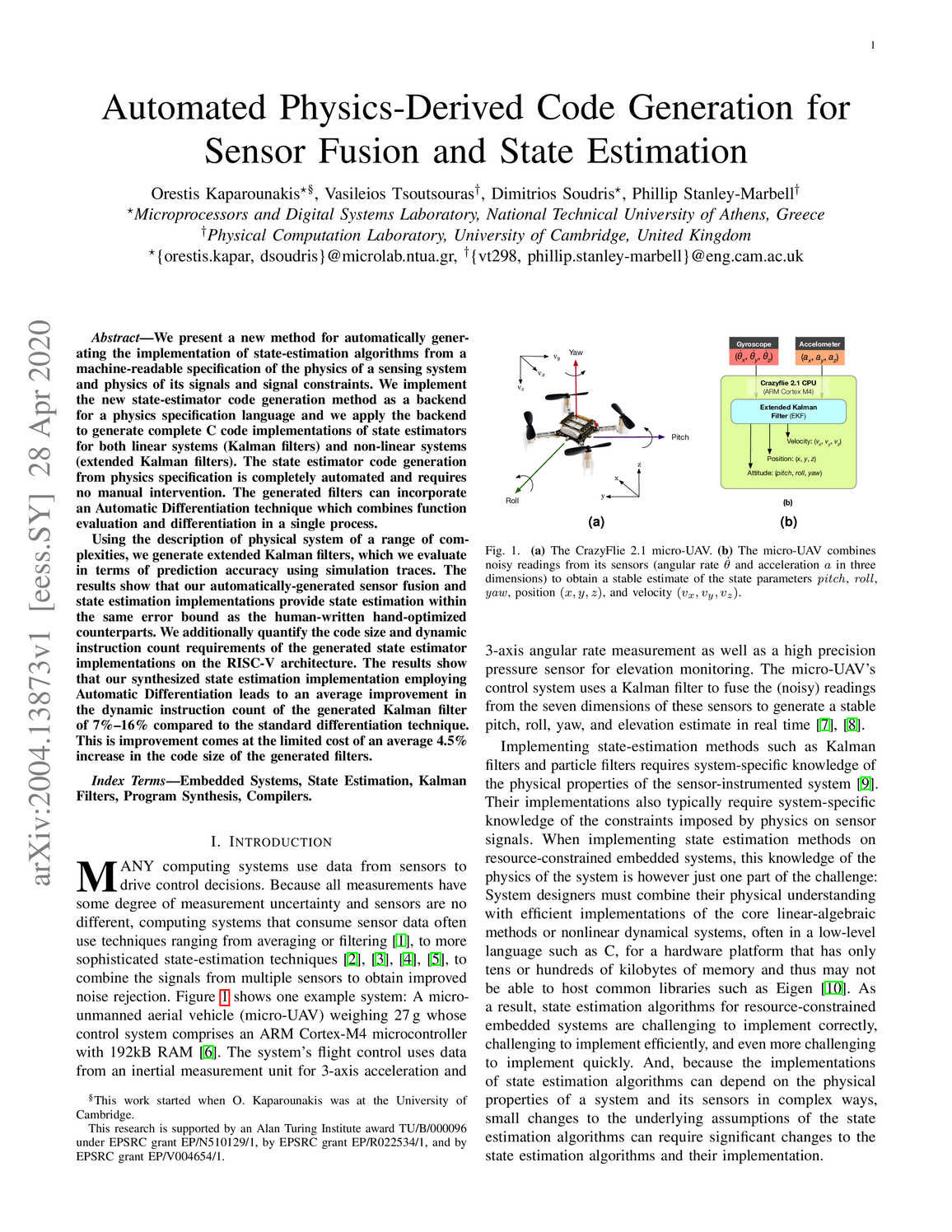

We present dimensional circuit synthesis, a new method for generating digital logic circuits that improve the efficiency of training and inference of machine learning models from sensor data. The hardware accelerators that the method generates are compact enough (a few thousand gates) to allow integration within low-cost miniaturized sensor integrated circuits, right next to the sensor transducer. The method takes as input a description of physical properties of relevant signals in the sensor transduction process and generates as output a Verilog register transfer level (RTL) description for a circuit that computes low-level features that exploit the units of measure of the signals in the system.

We implement dimensional circuit synthesis as a backend to the compiler for Newton, a language for describing physical systems. We evaluate the backend implementation and the hardware it generates, on descriptions of 7 physical systems. The results show that our implementation of dimensional circuit synthesis generates circuits of as little as 1662 logic cells / 1239 gates for the systems we evaluate.

We synthesize the designs generated by the dimensional circuit synthesis compilation backend for a low-power miniature FPGA targeted by its manufacturer at sensor interface applications. The circuits which the method generated use as little as 27% of the resources of the 2.15x2.5 mm FPGA. We measure the power dissipation of the FPGA's isolated core supply rail and show that, driven with a pseudorandom signal input stream, the synthesized designs use as little as 1.0 mW and no more than 5.8 mW. These results show the feasibility of integrating physics-inspired machine learning methods within low-cost miniaturized sensor integrated circuits, right next to the sensor transducer.

Cite as:

Tsoutsouras, V., Vigdorchik, M., & Stanley-Marbell, P. (2020). Synthesizing Compact Hardware for Accelerating Inference from Physical Signals in Sensors. ArXiv, abs/2002.01241.

BibTeX:

@misc{tsoutsouras2020synthesizing,

title={Synthesizing Compact Hardware for Accelerating Inference from Physical Signals in Sensors},

author={Vasileios Tsoutsouras and Max Vigdorchik and Phillip Stanley-Marbell},

year={2020},

eprint={2002.01241},

archivePrefix={arXiv},

primaryClass={cs.AR}

}